- 您现在的位置:买卖IC网 > Sheet目录323 > EFM32G-DK3550 (Energy Micro)KIT DEVELOPMENT EFM32 GECKO

...the world's most energy friendly microcontrollers

Bit

Name

Reset

Access

Description

Enable interrupt on overflow

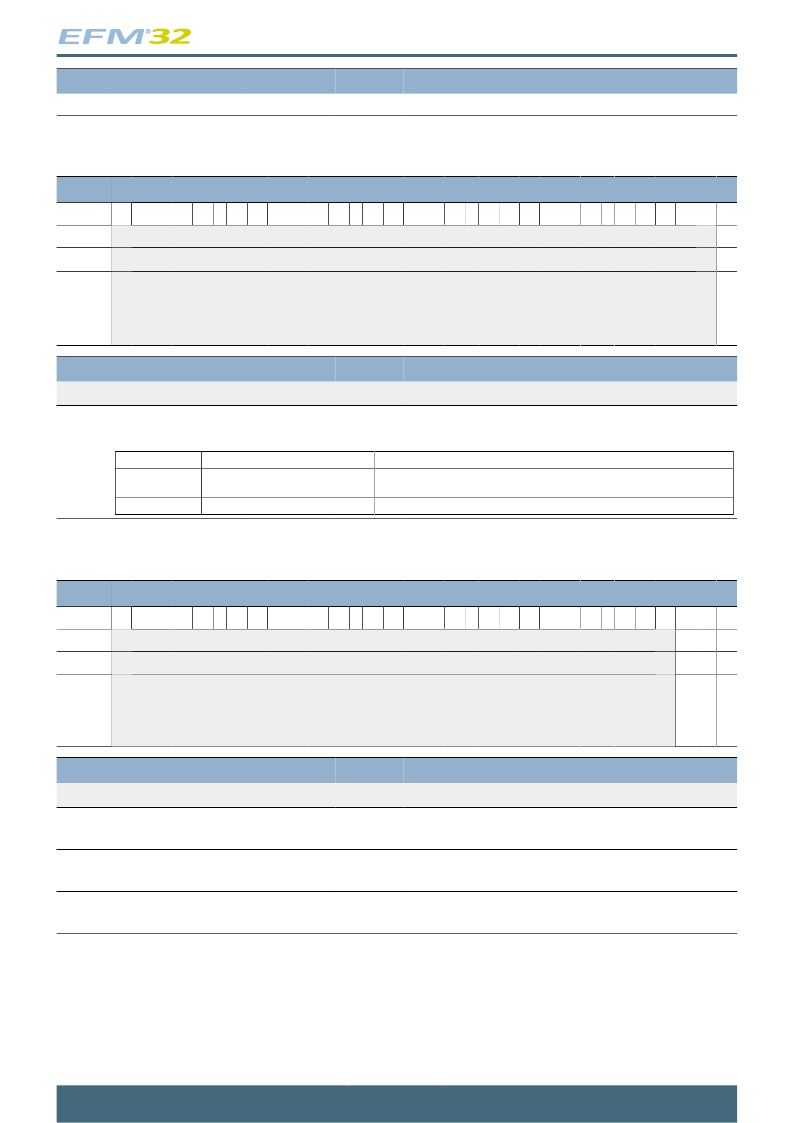

20.5.9 RTC_FREEZE - Freeze Register

Offset

0x020

Reset

Access

Name

Bit Position

Bit

Name

Reset

Access

Description

31:1

Reserved

To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3)

0

REGFREEZE

0

RW

Register Update Freeze

When set, the update of the RTC is postponed until this bit is cleared. Use this bit to update several registers simultaneously.

Value

0

1

Mode

UPDATE

FREEZE

Description

Each write access to an RTC register is updated into the Low Frequency domain as

soon as possible.

The RTC is not updated with the new written value until the freeze bit is cleared.

20.5.10 RTC_SYNCBUSY - Synchronization Busy Register

Offset

0x024

Reset

Access

Name

Bit Position

Bit

Name

Reset

Access

Description

31:3

Reserved

To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3)

2

COMP1

0

R

RTC_COMP1 Register Busy

Set when the value written to RTC_COMP1 is being synchronized.

1

COMP0

0

R

RTC_COMP0 Register Busy

Set when the value written to RTC_COMP0 is being synchronized.

0

CTRL

0

R

RTC_CTRL Register Busy

Set when the value written to RTC_CTRL is being synchronized.

2011-04-12 - d0001_Rev1.10

286

www.energymicro.com

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EFM32GG-STK3700

KIT STARTER GIANT GECKO

EFM32LG-DK3650

KIT DEV EFM32 LEOPARD GECKO

EK-K7-KC705-CES-G-J

KINTEX-7 FPGA KC705 EVAL KIT

EK-S6-SP601-G

KIT EVAL SPARTAN 6 SP601

EK-S6-SP605-G

KIT EVAL SPARTAN 6 SP605

EK-V6-ML631-G-J

VIRTEX-6 HXT FPGA ML631 EVAL KIT

EK-V7-VC707-CES-G

VIRTEX-7 VC707 EVAL KIT

EK-Z7-ZC702-CES-G

ZYNQ-7000 EPP ZC702 EVAL KIT

相关代理商/技术参数

EFM32GG230F1024

功能描述:ARM微控制器 - MCU 1024KB FL 128KB RAM

RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 处理器系列:STM32F373xx 数据总线宽度:32 bit 最大时钟频率:72 MHz 程序存储器大小:256 KB 数据 RAM 大小:32 KB 片上 ADC:Yes 工作电源电压:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:LQFP-48 安装风格:SMD/SMT

EFM32GG230F1024G-E-QFN64R

功能描述:IC MCU 32BIT 1MB FLASH 64QFN 制造商:silicon labs 系列:Giant Gecko 包装:剪切带(CT) 零件状态:在售 核心处理器:ARM? Cortex?-M3 核心尺寸:32-位 速度:48MHz 连接性:I2C,IrDA,智能卡,SPI,UART/USART 外设:欠压检测/复位,DMA,POR,PWM,WDT I/O 数:56 程序存储容量:1MB(1M x 8) 程序存储器类型:闪存 EEPROM 容量:- RAM 容量:128K x 8 电压 - 电源(Vcc/Vdd):1.98 V ~ 3.8 V 数据转换器:A/D 8x12b,D/A 2x12b 振荡器类型:内部 工作温度:-40°C ~ 85°C(TA) 封装/外壳:64-VFQFN 裸露焊盘 供应商器件封装:64-QFN(9x9) 标准包装:1

EFM32GG230F1024-QFN64

制造商:Energy Micro AS 功能描述:GIANT GECKO MCU - Cut TR (SOS) 制造商:Energy Micro 功能描述:GIANT GECKO MCU 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 1MB FLASH 64QFN

EFM32GG230F1024-QFN64T

制造商:Energy Micro AS 功能描述:GIANT GECKO MCU - Trays

EFM32GG230F1024-QFN64-T

制造商:Energy Micro AS 功能描述:IC MCU 32BIT 1MB FLASH 64QFN

EFM32-GG230F1024-SK

制造商:Energy Micro AS 功能描述:GIANT GECKO SAMPLE KIT - Bulk

EFM32GG230F1024-T

制造商:Energy Micro AS 功能描述:IC MCU 32BIT 1MB FLASH 64QFN

EFM32GG230F512

功能描述:ARM微控制器 - MCU 512KB FL 128KB RAM

RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 处理器系列:STM32F373xx 数据总线宽度:32 bit 最大时钟频率:72 MHz 程序存储器大小:256 KB 数据 RAM 大小:32 KB 片上 ADC:Yes 工作电源电压:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:LQFP-48 安装风格:SMD/SMT